| 포스트 플래시 시대 여는 차세대 메모리 양산 임박 |

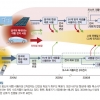

포스트 플래시 메모리와 포스트 DRAM의 자리를 노리는 차세대 메모리 개발 경쟁이 새로운 국면에 들어섰다. 저항 변화 메모리 즉, ReRAM(Resistance Random Access Memory)과 수직자화를 이용한 스핀 주입 방식의 MRAM(Magnetoresistive RAM) 등 새로운 메모리가 ISSCC(International Solid-State Circuits Conference)에 처음 등장했기 때문이다. ISSCC는 일정 규모 이상의 칩 샘플 제작이 반드시 수반되어야 하는 반도체 회로 기술 관련 컨퍼런스로서, 이번 행사에서 소개된 차세대 메모리 기술들의 잠재 능력은 대부분의 엔지니어들의 예상을 뛰어 넘는 수준이었다.

용량·칩 면적에서도 우위 모토유키 오이시(Motoyuki Oishi) |

| 번호 | 제목 | 닉네임 | 조회 | 등록일 | |

|---|---|---|---|---|---|

| 19 |

|

Donkey RC카 프로젝트 [Raspberry Pi + Python (tensorflow, opencv, ....)] | |||

just4you |

17107 | 2018-08-24 | |||

|

RC카에 라즈베이파이를 얹어서 자율주행하는 프로젝트입니다. 라즈베리파이에 카메라를 달아서 이미지를 받아서 TensorFlow로 학습을 합니다. 이때 이미지 처리 라이브러리는 OpenCV를 사용하고요.. 괜찮은 프로젝트인듯한데... 한번쯤 소스 ...

|

|||||

| 18 |

|

EEG 인터페이스용 헤드셋과 SDK를 소개합니다.

|

|||

just4you |

28299 | 2013-06-17 | |||

|

이 회사는 2006년도 쯤부터 계속 주목하고 있는데..

헤드셋 + SDK의 조합으로 큰 변화는 없는 것같네요..

(내부적인 소프트웨어 업데이트는 계속 이루어 지고 있을겁니다)

그리고 개발자들이 접근하기에 현실적인 가격이 가장 큰 메리트입...

|

|||||

| 17 |

|

LG 차세대 옵티머스G2폰 살짝 공개

|

|||

anymodules |

19689 | 2013-01-06 | |||

|

LG전자의 차세대 스마트폰 옵티머스G2에 대한 관심이 집중되고 있으나 CES2013에서는 볼 수 없을 전망이다. 외신은 LG전자의 CES2013 동영상 속 스마트폰을 옵티머스G2로 추정하며 LG전자의 차세대 스마트폰을 기대하고 있다. 슬래시기어 ...

|

|||||

| 16 |

|

저렴한 ARM MCU 보드들을 소개합니다. [1] | |||

just4you |

34611 | 2012-10-15 | |||

|

임베디드에 입문하시는 분들을 위해 저렴한 ARM MCU 보드를 소개합니다.

- STM32F4-Discovery

관련 사이트 http://www.st.com/stm32f4-discovery

마우져(www.mouser.com)에서 1.8만원에 구매가능합니다.

저가형 개발보드의 원조라고 할 ...

|

|||||

| 15 |

|

`감탄! 옵티머스G`…진짜 놀라운 이 기능

|

|||

anymodules |

22163 | 2012-09-18 | |||

|

`감탄! 옵티머스G`…진짜 놀라운 이 기능 `뛰어난 디스플레이` 선명도 스마트폰중 최고 곡선형태 후면 디자인 그립감 뛰어나 김유정 기자 clickyj@dt.co.kr | 입력: 2012-09-18 20:16[2012년 09월 19일자 3면 기사] 곡선형태 후면 디자인 ...

|

|||||

| 14 |

|

“전기 자동차의 대항해 시대가 코앞에!” (II)

|

|||

anymodules |

23434 | 2012-08-22 | |||

|

신형 Tesla EV 등장 전망 한편 Tesla사에서는 자사 차량용의 기술을 계속해서 개선해 왔으며, 10만 달러가 넘었던 오리지널 Roadster EV보다 훨씬 저렴한 가격으로 구상중인 차량의 개발에 착수했다고 JB Straubel 씨는 말했다. 내년에 ...

|

|||||

| 13 |

|

LG그룹, `자동차` 넘본다..현대차그룹 긴장

|

|||

etre21c |

28648 | 2012-02-13 | |||

|

출처 : http://www.edaily.co.kr

LG그룹, `자동차` 넘본다..현대차그룹 긴장전기차 배터리에 자동차 설계·부품, 카쉐어링까지 진출 구본무 회장 지시로 그룹 차원서 추진..현대차 속내 불편 LG 유플러스, 카쉐어링 업체 지분투자 추진 [이데...

|

|||||

| 12 |

|

LG전자 안승권 사장, “올해 TV 트렌드는 3D 대형화”

|

|||

anymodules |

29010 | 2012-01-12 | |||

|

LG전자 안승권 사장, “올해 TV 트렌드는 3D 대형화”

게재: 2012년01월11일

-->

LG전자가 현지시각 9일 미국 라스베이거스 베네시안 호텔에서 ‘LG전자 프레스 컨퍼런스’를 열고 전략제품과 혁신기술을

소개했다. LG전자 최고기술책임...

|

|||||

| 11 |

|

프리스케일, 차세대 i.MX 제품용 ARM Cortex-A7 및 Cortex-A15 프로세서 코어 라이센스 취득 | |||

anymodules |

23605 | 2011-11-17 | |||

|

프리스케일, 차세대 i.MX 제품용 ARM Cortex-A7 및 Cortex-A15 프로세서 코어 라이센스 취득 프리스케일, 차세대 i.MX 제품용 ARM Cortex-A7 및 Cortex-A15 프로세서 코어 라이센스 취득 임베디드, 자동차 및 스마트 모바일 디...

|

|||||

| 10 |

|

주파수 '뜨거운 감자' 700㎒ 용도 내달 확정 | |||

dwkim |

19364 | 2011-11-09 | |||

|

발행일 2011.11.08 이호준기자 newlevel@etnews.com 정부가 주파수 가용자원 가운데 '뜨거운 감자'로 꼽히는 700㎒ 대역 용도를 다음 달 확정한다. 700㎒에 눈독을 들여온 통신업계와 방송업계 사이에 마지막까지 치열한 주파수 확보 공방...

|

|||||

| 9 |

|

아이폰4 전파인증 접수…8월 27일 출시

|

|||

anymodules |

24874 | 2010-07-30 | |||

|

아이폰4 전파인증 접수…8월 27일 출시 지면일자 2010.07.30 박창규기자 dkseo@etnews.co.kr ▶ 기자의 다른 기사 보기 한마디쓰기(0) -작게 | 기본 | +크게 애플 아이폰4가 다음달 27일 전후로 공식 출시된다. 애플은 29일 오전 11시30분...

|

|||||

| 8 |

|

애플 '안테나 게이트' 점입가경

|

|||

dwkim |

26036 | 2010-07-27 | |||

|

애플 '안테나 게이트' 점입가경 지면일자 2010.07.27 이은용기자 eylee@etnews.co.kr ▶ 기자의 다른 기사 보기 한마디쓰기(0) -작게 | 기본 | +크게 애플이 공개한 RIM `블랙베리 볼드 9700`의 수신 세기 감쇄 동영상. 애플 ‘아이폰4’...

|

|||||

| 7 |

|

EV 및 대형 축전지 용도로 고체 전해질 전지에 관심 급증

|

|||

dwkim |

25348 | 2010-07-26 | |||

|

EV 및 대형 축전지 용도로 고체 전해질 전지에 관심 급증전기 자동차(EV)와 정치형 축전 용도의 대형 전지에 대한 수요가 급격히 늘어나고 있는 가운데 기존의 유기 전해질 대신 고체 전해질을 사용하는 전지에 대한 관심이 높아지고 ...

|

|||||

| 6 |

|

3D 방송 표준 경쟁 본격 점화, MPEG2에서 H.264로의 이행도 관심사

|

|||

dwkim |

28459 | 2010-07-22 | |||

|

3D 방송 표준 경쟁 본격 점화, MPEG2에서 H.264로의 이행도 관심사2005년 무렵부터 시작된 3D 영상 붐이 드디어 방송으로까지 확대되기 시작했다. 1890년대부터 시작된 영상의 진화, 즉 무성 영화에서 유성 영화로, 흑백 TV에서 컬러 ...

|

|||||

| 5 |

|

애플의 아이패드 전격 해부, 하드웨어에 적용된 아이디어와 과제들

|

|||

dwkim |

25242 | 2010-07-21 | |||

|

애플의 아이패드 전격 해부, 하드웨어에 적용된 아이디어와 과제들휴대폰이나 PC 그 어느 것과도 다른 전혀 새로운 인터넷 단말기 시장이 생겨날 것인가? 애플이 출시한 '아이패드(iPad)'에 뜨거운 관심이 쏟아지고 있다. 이번 기사에서는...

|

|||||

|

|

포스트 플래시 시대 여는 차세대 메모리 양산 임박

|

|||

dwkim |

28063 | 2010-07-20 | |||

|

포스트 플래시 시대 여는 차세대 메모리 양산 임박포스트 플래시 메모리와 포스트 DRAM의 자리를 노리는 차세대 메모리 개발 경쟁이 새로운 국면에 들어섰다. 저항 변화 메모리 즉, ReRAM(Resistance Random Access Memory)과 수직자...

|

|||||

| 3 |

|

소셜 컴퓨팅과 프로세스 포퓰리즘

|

|||

dwkim |

29124 | 2010-07-18 | |||

|

[데스크칼럼]소셜 컴퓨팅과 프로세스 포퓰리즘 기사등록일 2010.07.19 한마디쓰기(0) -작게 | 기본 | +크게 “전통적인 비즈니스프로세스관리(BPM)는 가라. 이제 소셜 BPM이다.” 포레스터리서치가 지난달 말 발표한 ‘소셜 소프트웨어와 웹 ...

|

|||||

| 2 |

|

'오바마 폰' 블랙베리 전용숍 국내 첫 등장

|

|||

dwkim |

23423 | 2010-07-18 | |||

|

http://www.etnews.co.kr/news/detail.html?id=201007160120&portal=001_00001'오바마 폰' 블랙베리 전용숍 국내 첫 등장 기사등록일 2010.07.19 김동석기자 dskim@etnews.co.kr ▶ 기자의 다른 기사 보기 한마디쓰기(0) -작게 | 기본 | +크게...

|

|||||

| 1 |

|

역풍 맞는 아이폰4…“쓴소리 귀막은게 화근”

|

|||

dwkim |

24344 | 2010-07-18 | |||

|

http://www.hani.co.kr/arti/economy/it/430883.html역풍 맞는 아이폰4…“쓴소리 귀막은게 화근” 구본권 기자» 지난 16일(현지시각) 미국 캘리포니아주 쿠퍼티노 애플 본사에서 열린 기자간담회 현장에서 애플의 최고경영자 스티브 잡스가 아이폰...

|

|||||